+ 한국항공대학교 길현영 교수님의 컴퓨터구조론 과목 내용을 정리한 글입니다.

디지털 논리 회로

데이터 / 연산의 HW 구현

데이터: 전기 신호의 흐름을 기호화한 것이다.

=> 하나의 전기 신호는 0, 1로 표현하고, 여러 개를 합쳐서 표현할 수 있는 데이터의 범위를 확장한다.

연산: 논리 게이트(Logic gate)를 기본 단위로 하여 해당 연산 결과를 구할 수 있는 디지털 논리회로를 구축한 것이다.

논리 게이트

논리 회로의 기본 HW 소자(구성 단위)이다.

입력 단자의 값들에 따라 해당 논리 게이트(연산)의 논리 값을 출력 단자의 값(0, 1)으로 출력한다.

- 기본 논리 게이트 (연산): AND, OR, NOT, XOR

조합 논리 회로 (Combinational)

현재의 입력값에 의해서만 출력값이 결정되는 논리 회로이다.

저장장치(기억소자)가 없다.

논리게이트들의 조합으로 구성되어 있다.

ex) 가산기, 비교기, 디코더, 인코더, 멀티플렉서, 디멀티플렉서 등

순차 논리 회로 (Sequential)

저장장치(기억소자)가 존재한다.

- 기억소자 내 상태(state)가 존재한다.

=> Sequence(차례, 절차) 구현이 가능하다.

현재의 입력과 기억소자의 상태(값들)에 따라 출력이 결정된다.

기억소자 + 논리게이트들의 조합으로 구성된다.

클락 신호 사용 여부에 따라 동기식 / 비동기식으로 나뉜다.

- 동기식: 클락값이 1이 될 때, 입력값을 반영한다.

- 비동기식: 클락에 상관없이 입력값이 변하면 결과값 / 기억소자 상태에 반영한다.

ex) 레지스터

디코더 (Decoder)

입력단자 n개, 출력단자 2^n개를 갖는다.

- 입력단자의 값에 대한 모든 경우의 수를 출력한다.

출력단자 중 하나만 1로 출력한다. (나머지는 0)

- 1을 출력한다 = 출력단자의 활성화

명령어의 연산 부호 해독 등에 사용된다.

ex) 10 (2) 입력 -> 3번 출력단자 활성화

인코더 (Encoder)

입력단자 2^n개, 출력단자 n개를 갖는다.

입력단자 중 하나만 1로 입력한다. (나머지는 0)

=> 출력단자는 이에 해당하는 코드를 출력한다.

ex) x1만 1 (0010) 입력 -> 10 (2) 출력

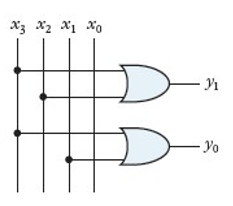

멀티플렉서 (MUX)

다수의 입력단자 중 조건에 맞는 하나를 선택하고 연결하는 조합회로이다.

- 선택 신호 s: 어떤 입력단자를 출력단자로 연결할지 결정한다.

ex) s = 00 => y = x0 (연결), s = 01 => y = x1 (연결), s = 10 => y = x2 (연결), s = 11 => y = x3 (연결)

Data selector: 2^n개의 입력단자 x, 1개의 출력단자 y를 갖는다.

디멀티플렉서 (DEMUX)

하나의 입력단자를 조건에 맞는 다수의 출력단자로 연결하는 조합회로이다.

- 선택 신호 s: 어떤 입력단자를 출력단자로 연결할지 결정한다.

ex) s = 00 => y0 = x (연결), s = 01 => y1 = x (연결), s = 10 => y2 = x (연결), s = 11 => y3 = x (연결)

반가산기

1 비트 단위의 덧셈을 수행한다. (하나의 자릿수만 계산)

- 결과값으로 1비트 합과 1비트 올림수 carry(out)를 갖는다.

전가산기

올림수 Carry(in)까지 포함하여 2비트 이상의 덧셈을 수행한다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [Computer Architecture] 데이터 경로 (0) | 2023.11.05 |

|---|---|

| [Computer Architecture] 데이터 연산 (picoMIPS) (1) | 2023.10.22 |

| [Computer Architecture] 데이터 표현 (1) | 2023.10.15 |

| [Computer Architecture] picoMIPS 명령어 집합 구조 (2) | 2023.10.15 |

| [Computer Architecture] CISC & RISC (49) | 2023.10.08 |